Introduction

The intention of this document is to get your familiar programming and using the Fipsy FPGA using a pre-built example – Blinky. The steps below will have you download the code, install the development tool, work with a project file, and upload the design to the FPGA.

This guide assumes you are programming the Fipsy with a Raspberry Pi. You can also program it with an Arduino. Click here to see your programming options.

Details on Fipsy FGPA are here.

Materials Needed

The materials you will need are:

- Fipsy FPGA

If you are able to write demo/training Verilog code examples & write-ups, request an early prototype by email: matt@mocomakers.com - A Raspberry Pi

Eg. https://amzn.to/2MTX6uk- To program via Arduino, or via USB on Windows, go here: https://www.mocomakers.com/fipsy-fpga/programmers/

- A Breadboard and Male-to-Female wires (I prefer a mix of male-to-male, and female-to-female wires)

Eg. http://amzn.to/2zjcclE

1. Get the Files

Download the project files here:

https://github.com/MocoMakers/Fipsy-FPGA-edu

2. Get Lattice Diamond

You will need to install Lattice Diamond, which is free but requires an account.

http://www.latticesemi.com/latticediamond

You will install Lattice Diamond on your primary computer, and Lattice Diamond supports Windows or Linux. Later you will transfer output files from this program to a Raspberry Pi to program the Fipsy.

3. Open the Lattice Project File

When you open Lattice Diamond, select Open Project, and navigate to FipsyBaseline_DiamondProject

Open the template Project File – FipsyBaseline.ldf

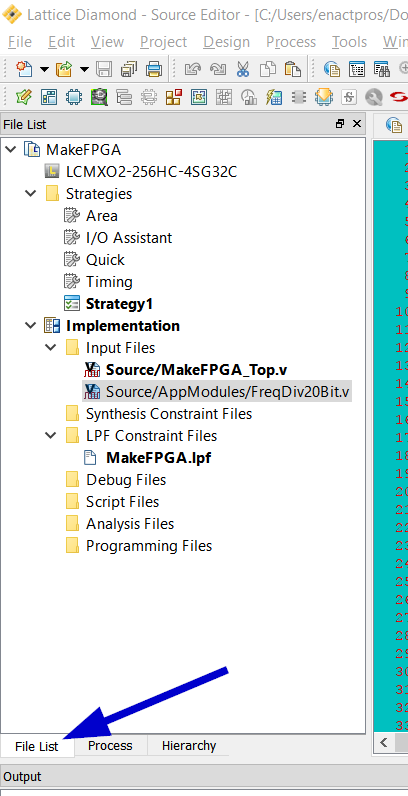

The file hierarchy can be found in the ‘File List’ tab:

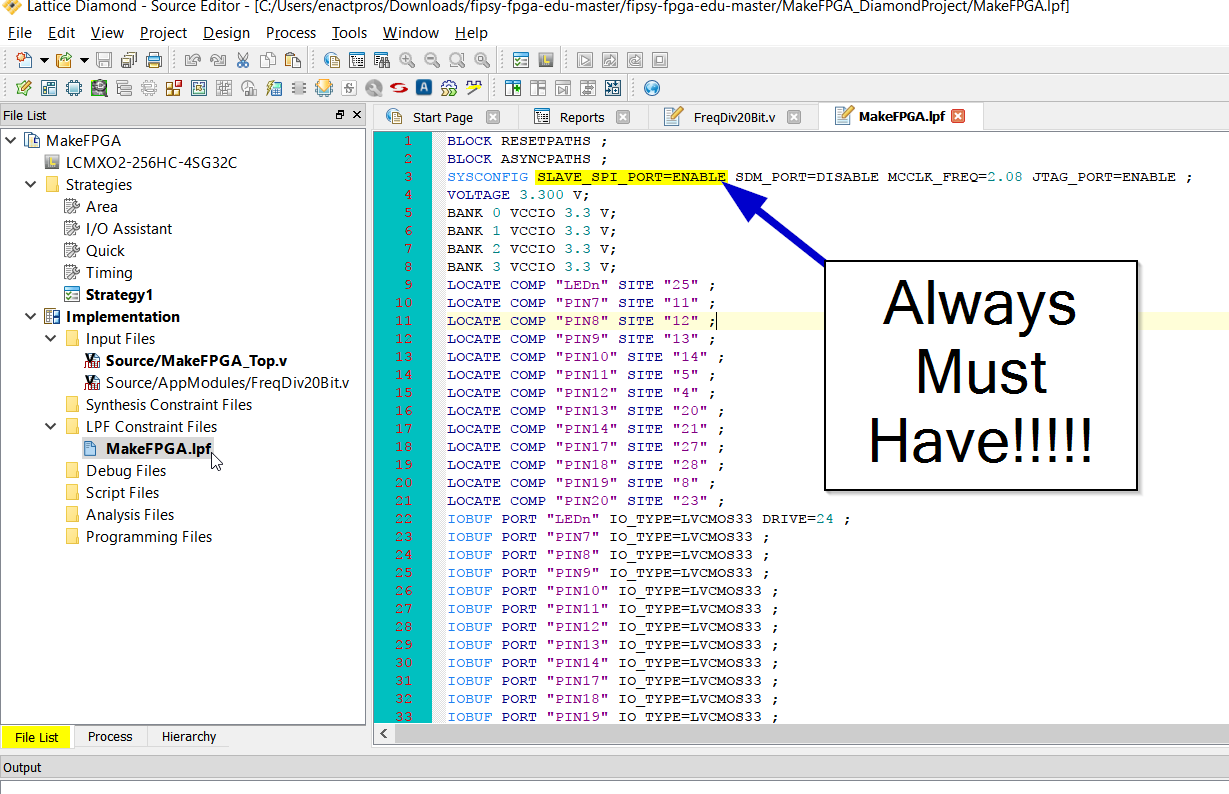

4. Check that SPI is Enabled

REQUIRED – If you ignore this, you might ‘Brick’ your FGPA

The SPI port (slave) is how we will program the FPGA, and it MUST stay enabled always. It is possible to ‘Brick’ or disable all future reproggramming, if the SPI port is not enabled. If you upload a design with SPI disabled, you will NOT be able to reprogram the FPGA again. Always keep SPI enabled:

Under ‘LPF Constraint Files’ check that your .lpf file has:

SYSCONFIG SLAVE_SPI_PORT=ENABLE

The easiest way to ensure this, is build your projects off of the template project file provided here. The programmers we provide have some built in checks to make sure you have this enabled.

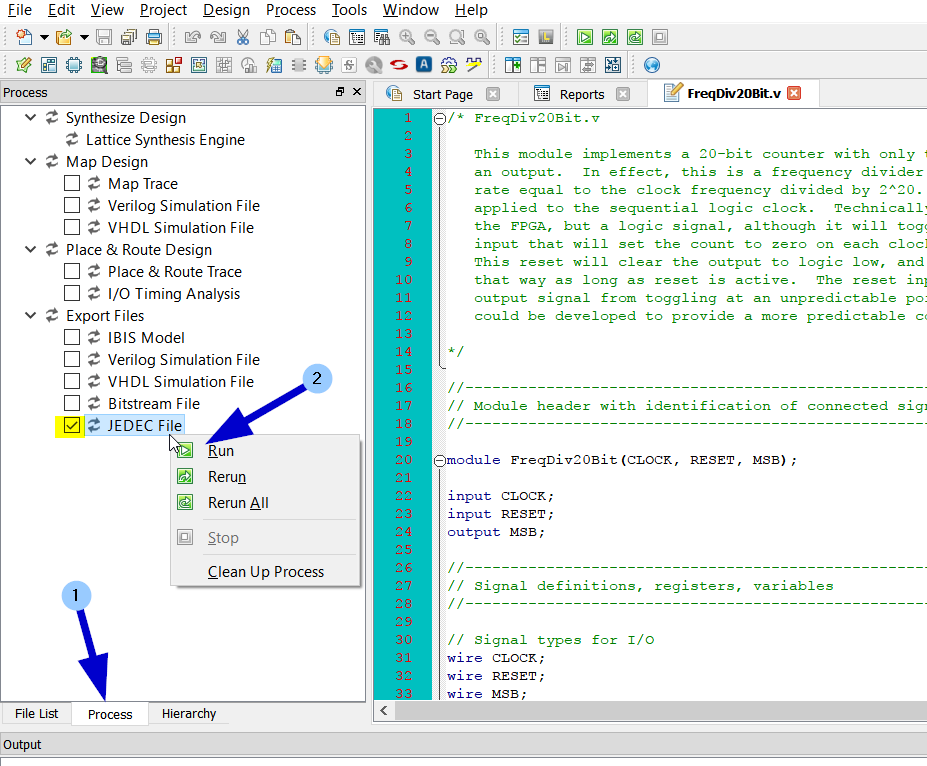

5. Create a JEDEC file

Click over to the next tab, and uncheck all boxes except the last one, JEDEC file. Right click and click RUN:

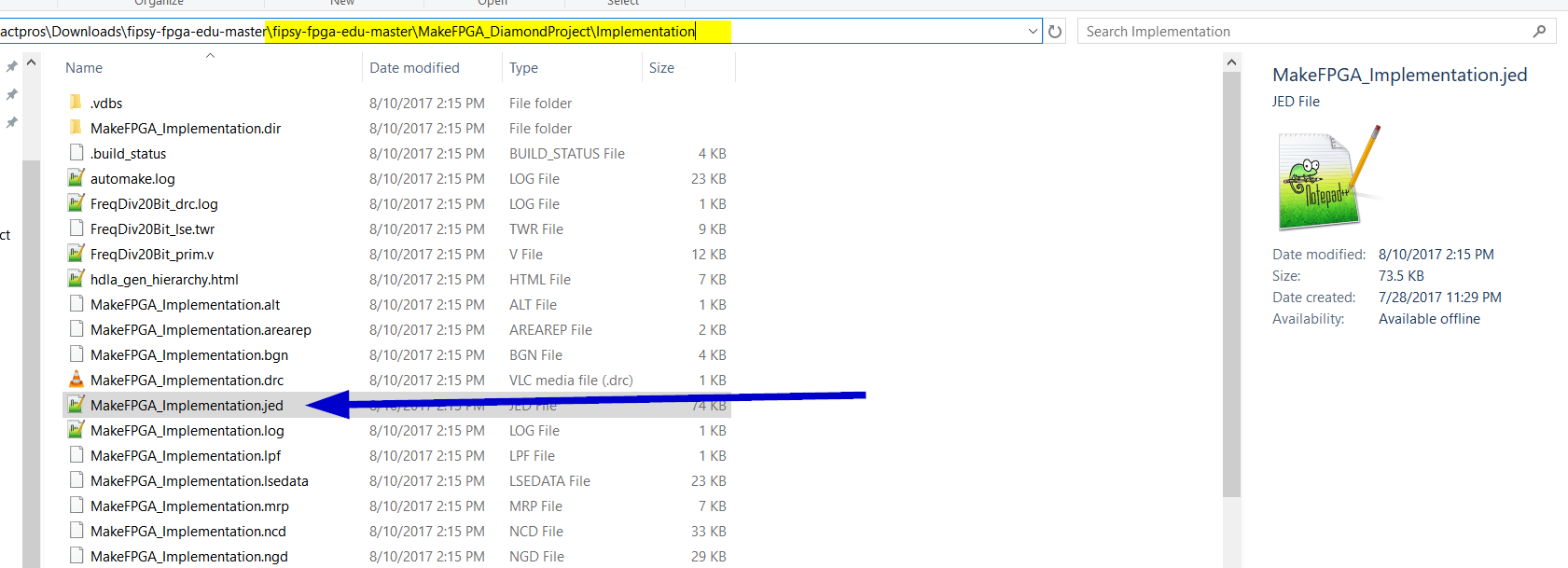

It will save a .jed file to the Implementations folder under the project folder:

6. SSH or log into your Raspberry Pi

Note that you will need your Pi to be connected to the internet, otherwise, you will have to transfer the example files via USB.

If you want to program with Arduino, or Windows-only, check out this page on other programmer options

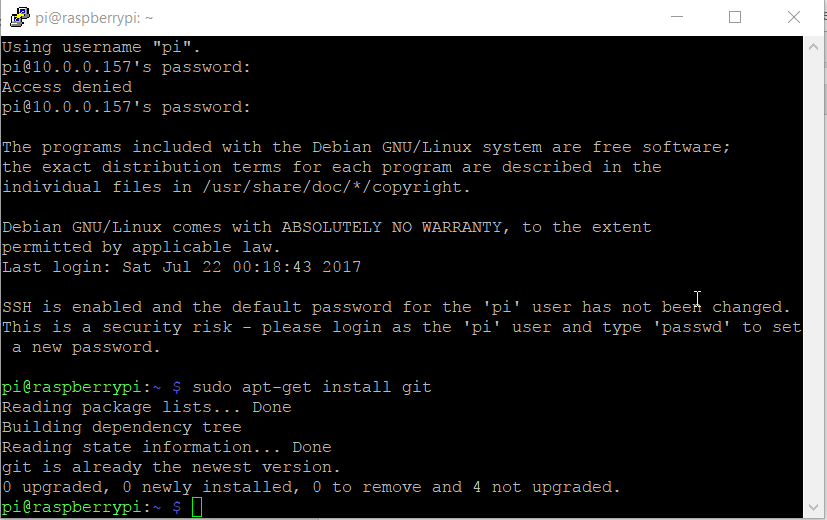

7. Install Git on Rasberry Pi

Install git with:

sudo apt-get install git

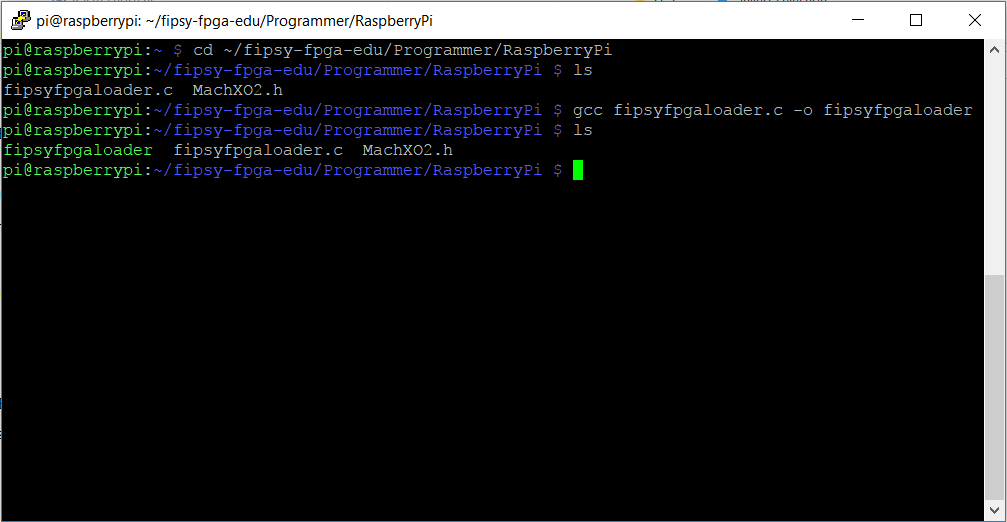

8. Compile the Raspberry Pi FPGA Programmer

Type:

1 2 3 4 5 6 | git clone https://github.com/MocoMakers/Fipsy-FPGA-edu cd ~/Fipsy-FPGA-edu/Programmer/RaspberryPi ls gcc fipsyloader.c -o fipsyfpgaloader ls |

Move the executable to the user desktop (or the folder where you want to have your .jed output files)

1 | cp ./fipsyfpgaloader ~/fipsyfpgaloader |

9. Set up your JEDEC File

Copy the JEDEC file (.jed) to the home directory:

1 2 3 | cd ~/Fipsy-FPGA-edu/FipsyBaseline_DiamondProject/Implementation cp FipsyBaseline_Implementation.jed ~/blinky2Hz.jed |

10. Enable the SPI port on your Raspberry Pi

SPI is used to program the Fipsy FPGA, and it must be enabled on the Raspberry Pi.

On the Raspberry Pi type:

1 | sudo raspi-config |

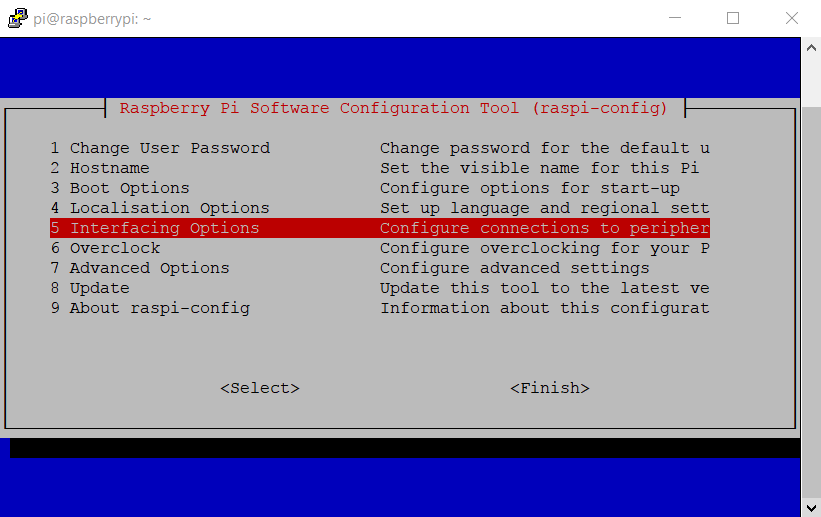

Next select ‘Interfacing Options’

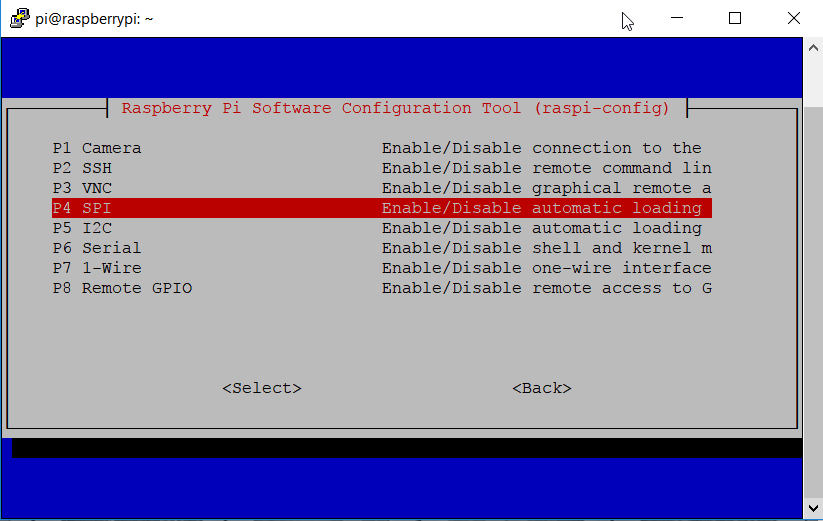

Go down to ‘SPI’ and select that option.

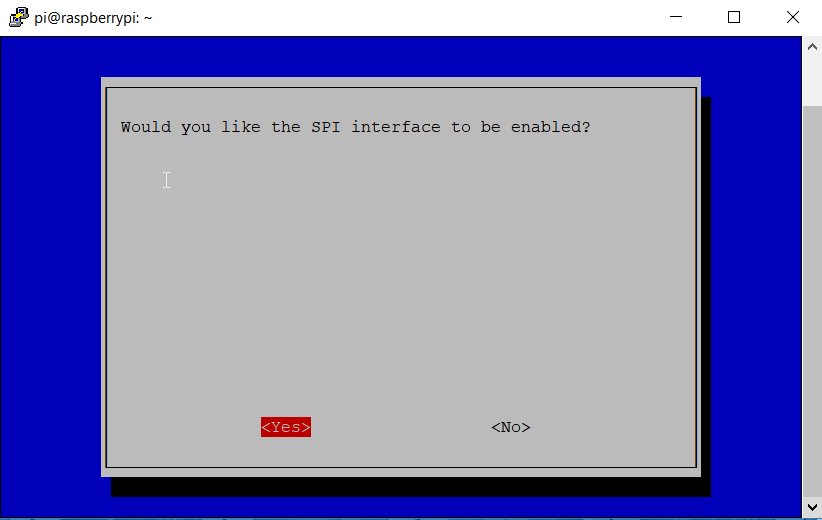

Select ‘Yes’ to enable the SPI

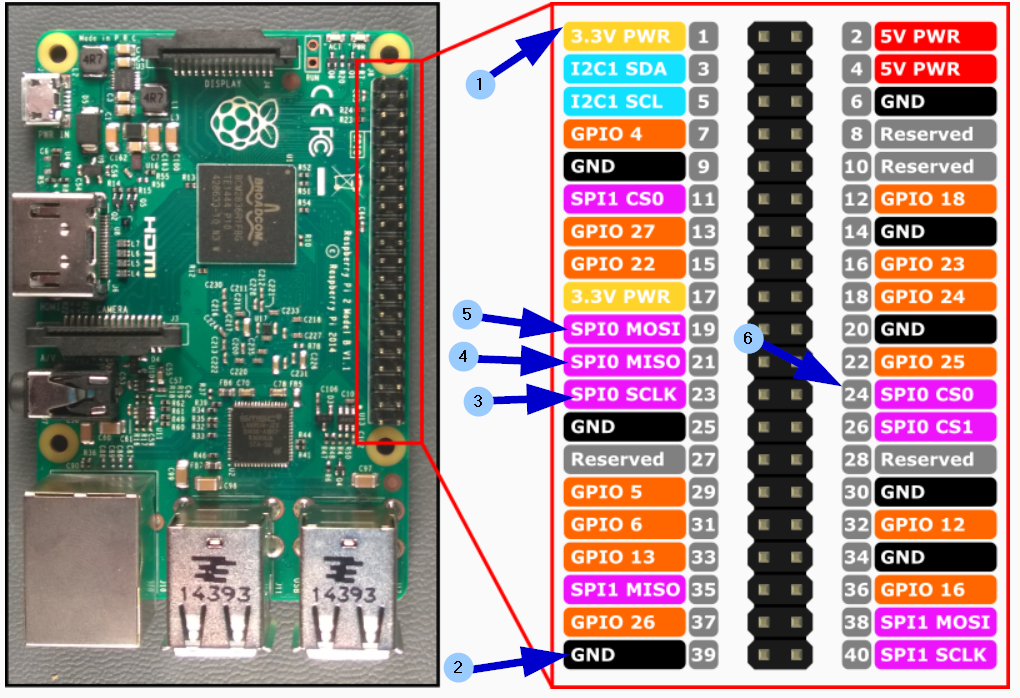

11. Wire up the Raspberry Pi:

Fispy FPGA -> Rasberry Pi

Pin 1 -> 3.3V (GPIO 1)

Pin 2 -> GND (GPIO 39)

Pin 3 -> SCLK (GPIO 23)

Pin 4 -> MISO (GPIO 21)

Pin 5 -> MOSI (GPIO 19)

Pin 6 -> CS0 (GPIO 24)

12. Run the Programmer on the JEDEC file (.jed)

On the raspberry pi type:

1 2 | cd ~ ./fipsyfpgaloader blinky2Hz.jed |

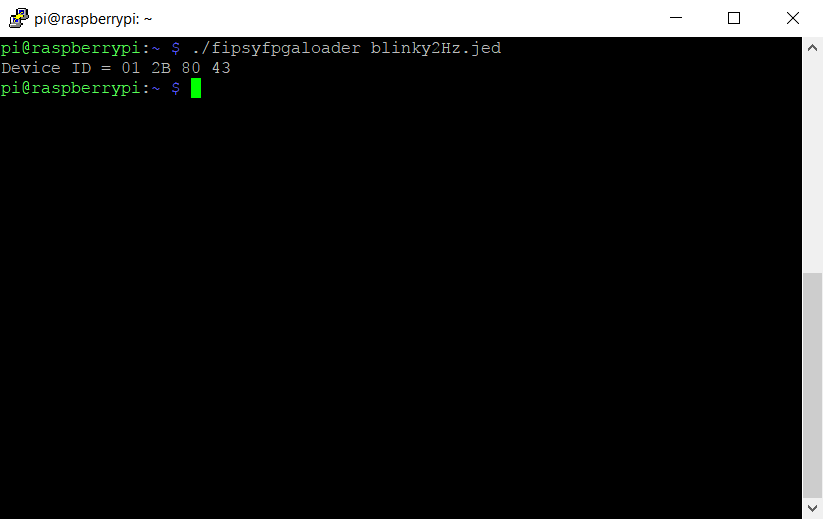

You should see something like this, except with your own unique manufacturer ID (on the FPGA itself).

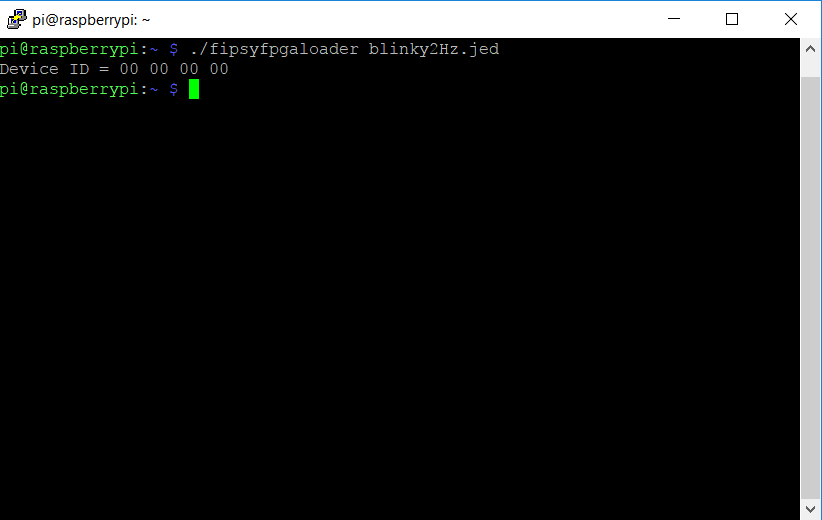

If you get all zeros for the Device ID, double check your wiring:

Congratulations, you are done!!

13. Getting additional .jed files onto the Raspberry Pi

There are many ways to get what is essentially a text file onto the Raspberry Pi (from the Lattice project’s ‘Implementation’ folder).

The easiest way is via SFTP, see item 5 on this guide:

http://www.makeuseof.com/tag/copy-data-raspberry-pi-pc/

You may want to set up a shared folder, for another elegant solution:

Setting up a shared folder between Raspberry Pi and Windows:

www.mocomakers.com/rapid-programming-with-fipsy-on-the-raspberry-pi/

Note that the fipsyfpgaloader you compiled above in step 8 is an executable file. That means you can copy to a shared directory you set up. The command to copy the executable would be

1 | cp /PATH_TO_FILE/fipsyfpgaloader /NEW/PATH/fipsyfpgaloader |

You could then change the the relevant folder:

cd /RELEVANT/PATH

and run the relevant ‘program FPGA’ command:

1 | ./fipsyfpgaloader NAME_OF_FILE.jed |

14. Continue Your Learning

Congratulations, you have uploaded your first configuration to an FPGA! Take a look at the example projects, and syntax guides we recomend on our wiki:

https://www.mocomakers.com/wiki/learning/

Additional Examples

Open the Lattice project mentioned above. This is the standard ‘Blinky’ example, which by default flashes at 2Hz (twice per second).

Notice that “Blinky_Rate_Divider.v” acts double the on/off time (so Blinky now flashes at 1Hz). It does this by inserting a flip/flop process.

Notice that “Blinky_Interrupt.v” builds on the above, turning PIN14 into an input for a button or switch. When the switch is turned on (3.3V is applied as an input), the blinking stops, until the switch is turned off or removed again.

That results in the following functionality:

| PIN14 | Flop2 | Output | LED State |

| 0 | 0 | 1 | Off |

| 0 | 1 | 0 | On |

| 1 | 0 | 1 | Off |

| 1 | 1 | 1 | Off |

Additional topics:

Flip Flop inspired by:

https://en.wikipedia.org/wiki/Verilog#Example

Useful Resources:

The Verilog code samples here:

http://academic.csuohio.edu/chu_p/rtl/fpga_vlog_book/fpga_vlog_src.zip

http://www2.dc.ufscar.br/~marcondes/netfpga/FPGAPrototypingByVerilogExamples.pdf

Intermediate Examples:

http://www.asic-world.com/examples/verilog/index.html

This Cheat Sheet is Great:

http://www.rrsg.uct.ac.za/courses/EEE4084F/Resources/Practicals/Prac5/Verilog%20Resources/Verilog_Cheat_Sheet.pdf

Alternate Cheat Sheets:

https://www.cl.cam.ac.uk/teaching/0910/ECAD+Arch/files/verilogcheatsheet.pdf

FIPSY FPGA Breakout Board – MoCo Makers

[…] Set-up software, and instrucitons can be found here: Basic Setup […]

Fipsy is a $10 Breadboard-Friendly FPGA Board for Education (Crowdfunding)

[…] “Basic Setup” tutorial explains how to create a Blinky example, by first creating a JEDEC file in Lattice Diamond […]